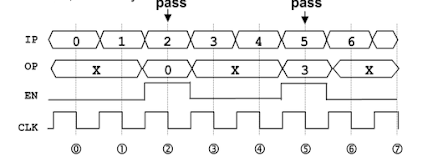

Nonconsecutive Repetition :

- Repeated, Nonconsecutive Boolean expressions can be defined using [=N]

- Nonconsecutive - Not necessarily consecutive

- Syntax : expr[=N]; expr must occur N times

- Example : When A is high then from the same cycle , there must be two cycles of B before C

property NONCONSECUTIVE_REPET;

@(negedge CLK) A |-> B[=2] ##1 C;

endproperty

assert property (NONCONSECUTIVE_REPET);

Note: In Non Consecutive Repetition Sequence , here there is no restrictions of number of cycles between second B and C.

Go-To Repetition :

- Syntax : expr[->N]

- Go to repetition operator is similar to the Nonconsecutive operator except expr must be true in the last cycle of the sequence

- Example : When A is high then from the same cycle , there must be two cycles of B before C , with C immediately following the second B

property GOTO_REPET;

@(negedge CLK) A |-> B[->2] ##1 C;

endproperty

assert property (GOTO_REPET);

Note: Last occurrence of B must be followed immediately by C

Hope, this blog post is helpful in understanding the tiny difference between these two operators while coding System Verilog Assertions.

Please like/share/comment and follow VLSI Excellence for such more interesting blog posts.

Happy Learning !!!