System Verilog Assertions - Useful Built-in Functions

$past() :

- Returns the value of a signal from previous evaluation cycle

- Syntax : $past (A, N) ; Default N = 1

- Example :

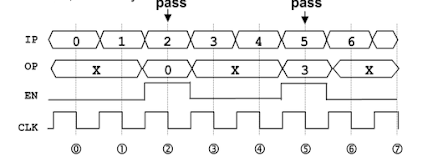

property PAST1;

@(negedge CLK) EN |-> (OP == $past(IP , 2 ));

endproperty

assert property (PAST1);

$stable() :

- Returns a Boolean True value if expr has the same value as it did in the previous cycle.

- Syntax : $stable(expr)

- Example :

property STABLE;

@(negedge CLK) ~ENAB |=> $stable(DOUT);

endproperty

assert property (STABLE);

$countones() :

- Returns the number of 1's in expr

- Any value other than 1 is ignored

- Syntax : $countones(expr)

- Example :

property 1HOT_CHK;

@(negedge CLK) ($countones(B_VECTOR) == 1);

endproperty

assert property (1HOT_CHK);

$isunknown() :

- Returns a Boolean True if any bit in expr is 'x' or 'z'

- Syntax : $isunknown(expr)

- Example :

property CHK_UNKNOWN;

@(negedge CLK) (~EN |=> $isunknown(B_VECTOR));

endproperty

assert property (CHK_UNKNOWN);

- When EN is low, check that any bits of B_VECTOR is driven as 'x' OR 'z'

$onehot() :

- Returns a Boolean True only if exactly one bit in expr is 1

- Syntax : $onehot(expr)

- Example :

property ONEHOT;

@(negedge CLK) ($onehot(B_VECTOR));

end property

assert property (ONEHOT);

$onehot0() :

- Returns a Boolean True only if, at most, 1 bit in expr is 1

- Syntax : #onehot0(expr)

- Example :

property ONEHOT0;

@(negedge CLK) ($onehot0(B_VECTOR));

endproperty

assert property (ONEHOT0);

$rose() :

- Click Here

$fell() :

- Click Here

Hope, this blog post is helpful in understanding the useful System Verilog built-in functions.

Please do like/share/comment and follow VLSI Problems for such more interesting blog posts.

Happy Learning !!!

Comments

Post a Comment