Time Borrowing in VLSI Design

Time Borrowing in VLSI Design : Here is the insights on what does the terminology "Time Borrowing" mean in VLSI Design, its implementation concepts and what all problems can be solved using time borrowing concepts. Everything you need to know about time borrowing? Please go through this page.

Time Borrowing Concept : Time borrowing concept is associated with Latch Based Designs.

Property of Latch : Data can pass through Latch while the Latch is Transparent. Whenever the clock is enabled the latch will work for a half period of time depending upon the polarity.

Latch Based Design: If there is a large combinational logic present in the design then it can borrow the time from the next cycle. So latch based designs are used, where we want the high performance of the design.

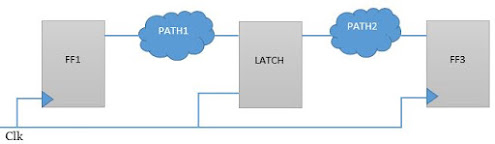

Lets have a look at below circuit diagram -

Lets assume, the clock period is 10ns. Setup, Hold, Clcok Skew, Clock Delay all are 0ns

What if the combinational delay for path (PATH1) is grater than 10ns ?

If combinational delay of PATH1 is greater than 10ns then FF2 can't capture the correct data because data is reaching at FF2 after 12ns and here occurs the setup violation.

Lets see how this violation can be removed using a Latch based approach.

If data reaches to the latch input before 10ns, this data waits at the latch’s D pin. This is a similar case as if we are using FF in place of latch.

If the data is coming after 12 ns then there is a problem if we are using a flip-flop. But if we use a Latch then there is no problem as we can see that the Latch is transparent from 10 -15 ns window and no problem to receive the data so we can receive our data by borrowing the time from the next clock cycle.

Note: The maximum time we can borrow from the Latch here is 5 ns.

For the Latch to FF3 path, Once the Latch launces the data ,it should reach to the FF3 before the next clock edge (.i.e @20ns )

As we see in above waveform, if the Flip-Flop setup time is 0ns then the data from Latch to the FF3 should reach in 8 ns (.i.e PATH2 maximum delay <= 8ns )

Comments

Post a Comment