1) Do we need any isolation strategy between ON - to - OFF (Standby) Block ? - Generally the isolation is required between OFF - to ON Block but in some cases it is recommended to use isolation between ON - to -OFF domain as well. - Normally the isolation strategy between OFF - to - ON is called as Parking - This kind of strategy is required for some special kind of signals which have...

Saturday, July 31, 2021

Fundamentals of LINT

Lint : - A Static analysis of code (e.g HDL) based on a series of rules and guidelines that reflect good coding practices, common errors that tend to lead to buggy code or problems - Lint tools are used to check potential mismatches between simulation and synthesis in VLSI Design - Lint incorporates syntactical compliance checks against various coding best practice standards such...

Fundamentals of Isolation Cells in Low Power VLSI Design

In Multi Voltage VLSI Design, isolation cells play an important role in the modern VLSI world.Requirement : Lets have a look at the below diagram - - Lets assume VDDA voltage domain is always ON and VDDB voltage domain can go ON or OFF based on the certain design requirements ( To minimize the...

Thursday, July 29, 2021

Digital Circuit Design - Problem#5

Problem: Design a digital circuit which can generate a pulse which is high for 16 clock cycles and then goes low (Active High Reset Signal)as shown in the below waveform Solution : - Lets have a look at previous problem where we discussed on how can we generate an active low reset...

Digital Circuit Design - Problem#4

Problem : Design a digital logic circuit to generate a reset pulse which is low for 16 clock cycles (Active Low Reset Generation) as shown in below waveform. Solution : - Here we need a output signal of the circuit which is low for 16 cycles and then becomes high - Can 16 flop in a cascade manner do...

Digital Circuit Design - Problem#3

Problem : Design a digital logic circuit to generate a stick bit as shown in the below waveform. The circuit takes an input as I/P and runs at a clock speed of CLK Solution : - Once the input is high the output should always remain high irrespective of whether the I/P signal is toggling at later point...

Wednesday, July 28, 2021

Digital Circuit Design - Problem#2

Problem : Design a black box circuit shown below whose input clock and output relationship is shown in below waveform. Solution : - Lets have a look at below circuit diagram - - Now lets see how the waveform looks like for this circuit - ...

Digital Circuit Design - Problem#1

Problem : Design a digital circuit as depicted in below block diagram which takes DIN as an input and runs at a clock speed of CLK and generates an output DATA as shown in the waveform below.Solution : - Since the circuit sample the data at both positive and negative edge of the clock, we need both...

Tuesday, July 27, 2021

Verilog HDL Examples - Design of an Event Detector (Circuit Design)

Problem : Design a circuit which detects and event (for one clock cycle) whenever there is a change (Either rising edge or falling edge)in the input signalSolution : 1) The input signal is asynchronous to the Event Detector logic domain -Note: The data_in must come out of a register from the source...

Monday, July 26, 2021

Tic-Tac-Toe Game Design Using Python

And here comes some fun in the time when we all are locked inside our homes because of this COVID-19 pandemic ( 05/25/2020) . I am going to guide you on how you can build your own Tic_Tac_Toe Game using Python scripts in just few minutes and can enjoy playing with your loved once.How to play Tic_Tac_Toe...

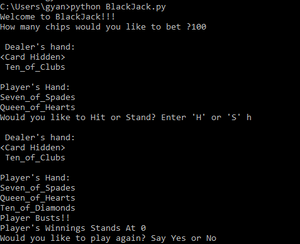

BlackJack Game Design Using Python

CASINO !!! Yes , You imagined Rightly. Let's see how in couple of minutes you can develop your own Black Jack Game using Python Scripting.Blackjack : Blackjack, formerly also Black Jack and Vingt-Un, is the American member of a global family of banking games known as "Twenty - One", whose relatives...

Thursday, July 22, 2021

Verilog HDL Examples - Design of Gray Code Counter (For FIFO Design)

Gray Code : - Named after Frank Gray- Known as reflected binary code (RBC), - Also known just as reflected binary (RB) or Gray Code - An ordering of the binary numeral system such that two successive values differ in only one bit (binary digit) Decimal(Base 10) Binary...

Data-To-Data [Non-Sequential] Timing Checks

Data To Data Timing Checks : - Setup and hold checks between two data pins (neither of these is defined as a clock) - Also referred as Non-Sequential Constraints - One data pin is the constraint pin , like a data pin of a flop and the second pin is the related pin which acts like a clock pin of a...

Wednesday, July 21, 2021

Verilog HDL Examples - FIFO Design - Asynchronous FIFOs

Asynchronous FIFO Design : - A FIFO Design where data values are written to a FIFO buffer from one clock domain and the data values are read from the same FIFO buffer from another clock domain - The clock domain are asynchronous to each other - Asynchronous FIFOs are used to safely pass the data...

Verilog HDL Examples - FIFO Design - Synchronous FIFOs

Synchronous FIFO Design : Lets have a look at below block diagram of Synchronous FIFO. Further we will have a look at its Verilog HDL implementation.For synchronous FIFO design (a FIFO where writes to, and reads from the FIFO buffer are conducted in the same clock domain),...

Monday, July 19, 2021

Bluetooth Low Energy - Link Layer Hardware Design : Architecture Overview

Link Layer Hardware Architecture : Lets have a look at the complete Bluetooth Low Energy (BLE) Stack Diagram below. Here, Application and Host of the BLE Stack are Software/Firmware component while Controller is a Hardware component. We will be focusing on the implementation of Link Layer (LL)...

System Verilog Assertions - Nonconsecutive Repetition

Nonconsecutive Repetition : - Repeated, Nonconsecutive Boolean expressions can be defined using [=N] - Nonconsecutive - Not necessarily consecutive - Syntax : expr[=N]; expr must occur N times - Example : When A is high then from the same cycle , there must be two cycles of B before C ...

System Verilog Assertions - Consecutive Repetition

Consecutive Repetition : - Repeated, consecutive sequences can be defined using [*N] - Syntax : SEQ[*N]; SEQ, repeated N times - Example : A is never low for more than 4 cycles property CONSECUTIVE_REPET; @(negedge...

Sunday, July 18, 2021

System Verilog Assertions - How it Works !!!

Here, is the flow diagram of how an assertion gets evaluated - Syntax : @(Clocking) disable iff (EXPR) enabling_sequence |=> fulfilling_sequence...

System Verilog Assertions - Sequences

System Verilog Sequences : - Temporal properties are described using sequences - Series of Boolean equations - Each cycle separated by ## - Syntax : SEQ_A |-> SEQ_B OR SEQ_A |=> SEQ_B - Properties are either unconditional using instantaneous Boolean expression ...

System Verilog Assertions - Example Problem

Problem: Write assertion(s) to verify the behavior of the below circuit - Solution:...

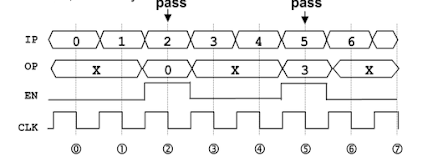

System Verilog Assertions - Useful Built-in Functions

$past() : - Returns the value of a signal from previous evaluation cycle - Syntax : $past (A, N) ; Default N = 1 - Example : property PAST1; @(negedge CLK) EN |-> (OP == $past(IP , 2 )); endproperty ...

Subscribe to:

Posts (Atom)